# Faux Vector Processor Design Using FPGA-Based Cores

by Diwas Timilsina

A thesis submitted in partial fulfillment of the requirements for the Degree of Bachelor of Arts with Honors in Computer Science

> Williams College Williamstown, Massachusetts

> > May 22, 2016

# Contents

| 1        | Intr                                          | roduction                                                                                                                                                                                                                                                     | 1                              |

|----------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 2        | Pre<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | vious Work         Efficiency Comparison Between GPPs, FPGAs, and ASICs         The Return of the Vector Processor         Performance- and Power-Improving Designs         GPP-FPGA Communication         Power Consumption Analysis on FPGA         Summary | 4<br>6<br>12<br>14<br>17<br>18 |

| 3        | <b>Τhe</b><br>3.1                             | e FPGA Work Flow<br>Field Programmable Gate Array Architecture                                                                                                                                                                                                | <b>20</b><br>21                |

|          | 3.2                                           | Architecture Supporting Partnered Communication                                                                                                                                                                                                               | 23                             |

|          | 3.3                                           | FPGA reconfiguration workflow                                                                                                                                                                                                                                 | 24                             |

|          |                                               | 3.3.1 Typical Application: Dot Product of Vectors                                                                                                                                                                                                             | 24                             |

|          |                                               | 3.3.2 Describing the Circuit                                                                                                                                                                                                                                  | 24                             |

|          |                                               | 3.3.3 Simulation                                                                                                                                                                                                                                              | 26                             |

|          |                                               | 3.3.4 Synthesis and Implementation                                                                                                                                                                                                                            | 27                             |

|          | 3.4                                           | Summary                                                                                                                                                                                                                                                       | 27                             |

| <b>4</b> | Fau                                           | x-Vector Processor                                                                                                                                                                                                                                            | 28                             |

|          | 4.1                                           | FVP Architectural Overview                                                                                                                                                                                                                                    | 29                             |

|          |                                               | 4.1.1 Interface                                                                                                                                                                                                                                               | 29                             |

|          |                                               | 4.1.2 Instruction Set Architecture                                                                                                                                                                                                                            | 31                             |

|          |                                               | 4.1.3 FPGA Implementation                                                                                                                                                                                                                                     | 35                             |

|          | 4.2                                           | Programming the FVP from Processing System                                                                                                                                                                                                                    | 37                             |

|          |                                               | 4.2.1 Design Examples                                                                                                                                                                                                                                         | 37                             |

|          | 4.3                                           | Summary                                                                                                                                                                                                                                                       | 43                             |

| 5        | Fau                                           | x-Vector Processor Performance Estimation                                                                                                                                                                                                                     | <b>45</b>                      |

| 0        | 5.1                                           | Methodology                                                                                                                                                                                                                                                   | 45                             |

|          | 5.2                                           | Hardware Utilization                                                                                                                                                                                                                                          | 45                             |

|          | 5.3                                           | Vector Performance                                                                                                                                                                                                                                            | 46                             |

|          | 5.4                                           | Benchmark Performance                                                                                                                                                                                                                                         | 53                             |

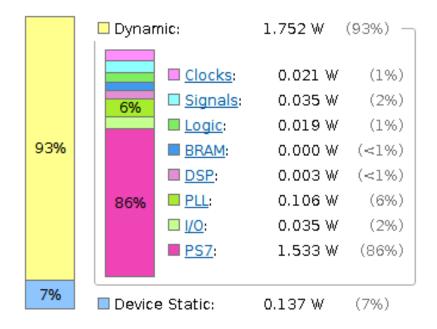

|          | 5.5                                           | Power Analysis                                                                                                                                                                                                                                                | 60                             |

|    | 5.6          | Summary                                        | 62 |

|----|--------------|------------------------------------------------|----|

| 6  | Futu         | ure Work                                       | 63 |

|    | 6.1          | Improving Faux-Vector Processor Design         | 63 |

|    |              | 6.1.1 Upgrading Memory Interface Unit          | 63 |

|    |              | 6.1.2 Broadening the Functionality             | 64 |

|    |              | 6.1.3 Multiple Lane Extension                  | 64 |

|    |              | 6.1.4 Integration with a Vector Compiler       | 64 |

|    |              | 6.1.5 Automating Circuit Design and Synthesis  | 65 |

|    | 6.2          | Improving Performance Estimation               | 65 |

|    |              | 6.2.1 Improved Power Analysis and Optimization | 65 |

|    | 6.3          | Open Challenges                                | 66 |

| 7  | Con          | clusions                                       | 67 |

| Ac | erony        | yms                                            | 68 |

| Bi | Bibliography |                                                |    |

# List of Figures

| 1.1  | 40 Years of trend in microprocessor data                                    | 2  |

|------|-----------------------------------------------------------------------------|----|

| 2.1  | GPP datapath energy breakdown                                               | 5  |

| 2.2  | Difference between scalar and vector Processor                              | 7  |

| 2.3  | The block diagram of VIRAM                                                  | 8  |

| 2.4  | The block diagram of CODE                                                   | 8  |

| 2.5  | The block diagram of Soft Core Processor                                    | 10 |

| 2.6  | VESPA architecture with two lanes                                           | 11 |

| 2.7  | The RSVP architecture                                                       | 12 |

| 2.8  | Diagram of a c-core chip                                                    | 13 |

| 2.9  | The block diagram of LegUp design                                           | 14 |

| 2.10 | The block diagram of RIFFA architecture                                     | 15 |

| 2.11 | Diagram of PuspPush Architecture                                            | 16 |

| 3.1  | Picture of Zedboard                                                         | 20 |

| 3.2  | Picture of FPGA                                                             | 22 |

| 3.3  | Xillybus overview                                                           | 23 |

| 3.4  | Implemented circuit diagram                                                 | 26 |

| 4.1  | Block diagram of FVP architecture                                           | 35 |

| 4.2  | Memory Interface Unit                                                       | 36 |

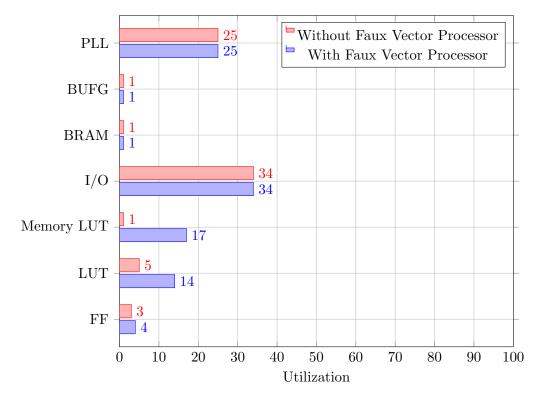

| 5.1  | Resource utilization of hardware implementation with and without FVP        | 46 |

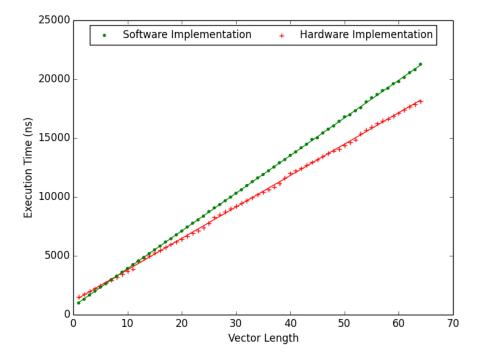

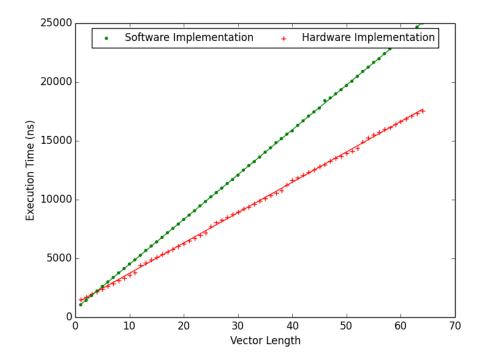

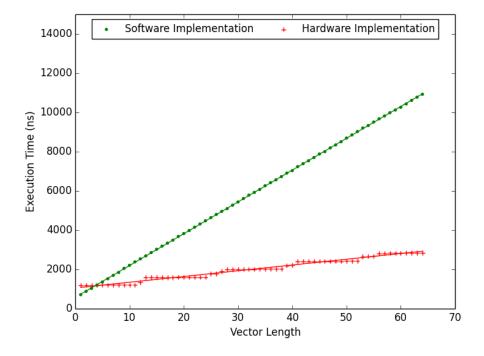

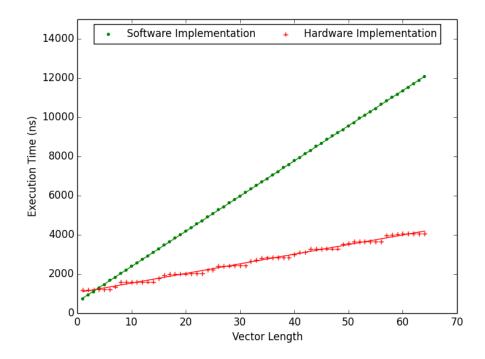

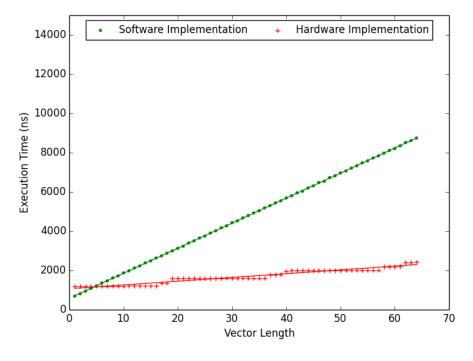

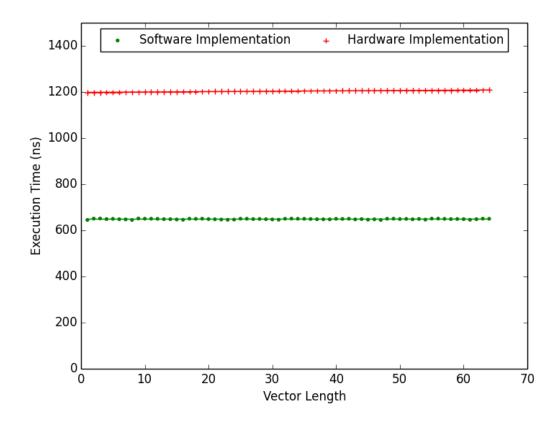

| 5.2  | Performance of VLD instruction                                              | 48 |

| 5.3  | Performance of VST instruction                                              | 48 |

| 5.4  | Performance of VADD instruction                                             | 49 |

| 5.5  | Performance of VMUL instruction                                             | 49 |

| 5.6  | Performance of VESHIFT instruction                                          | 50 |

| 5.7  | Performance of VMAC instruction                                             | 51 |

| 5.8  | Performance of VFAND operation                                              | 52 |

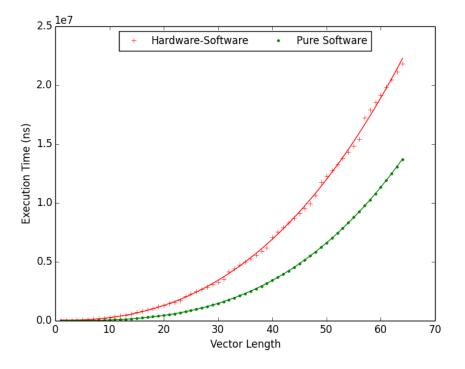

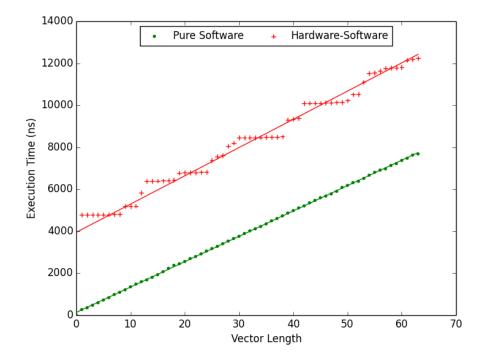

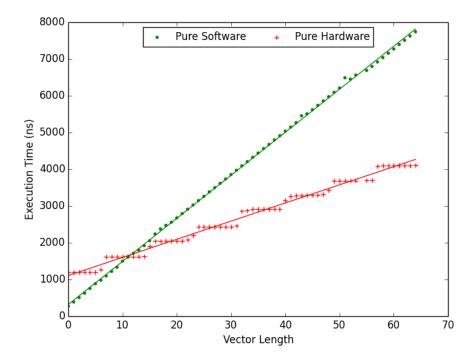

| 5.9  | Performance of matrix multiplication on hardware-software and pure software | 55 |

| 5.10 | Performance of SAXPY on hardware-software and pure software                 | 55 |

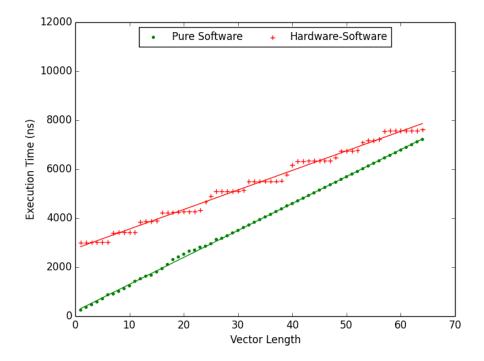

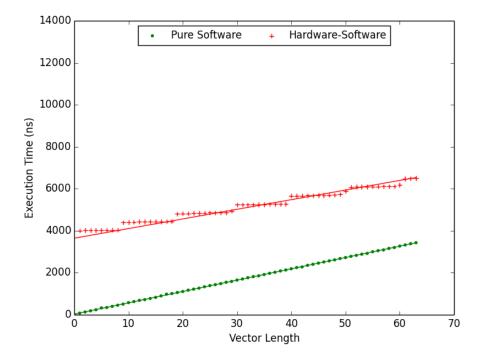

| 5.11 | Performance of FIR filter on hardware-software and pure software            | 56 |

| 5.12 | Performance of compare and exchange on hardware-software and pure software  | 56 |

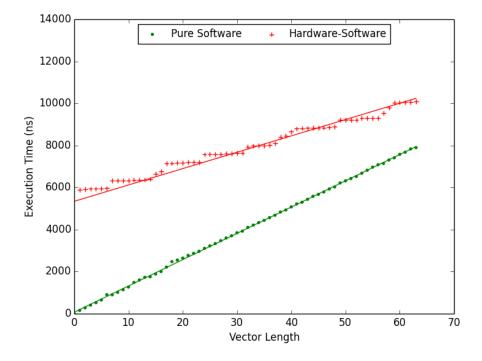

| 5.13 | Performance of string compare on hardware-software and pure software        | 57 |

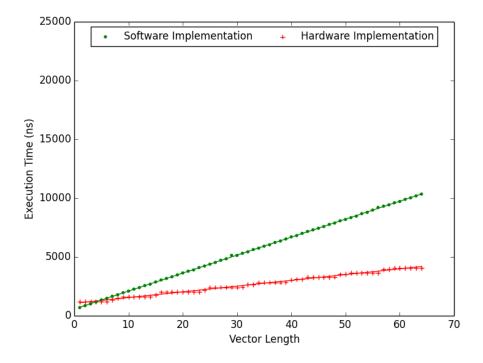

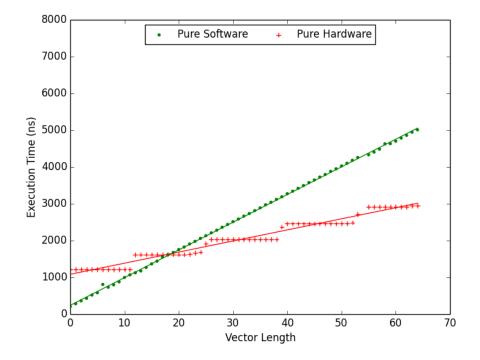

| 5.14 | Add performance on pure hardware vs pure software                 | 58 |

|------|-------------------------------------------------------------------|----|

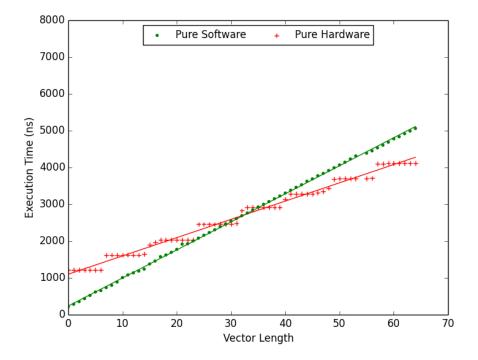

| 5.15 | Multiply performance on pure hardware vs pure software            | 59 |

| 5.16 | Multiply accumulate performance on pure hardware vs pure software | 59 |

| 5.17 | Power consumption on a transistor                                 | 60 |

| 5.18 | Power estimation using Vivado's Power Analysis Tool               | 61 |

| 5.19 | Power consumption on the hardware implementation                  | 61 |

## List of Tables

| 4.1  | List of parameters for the Faux Vector Processor        | 9 |

|------|---------------------------------------------------------|---|

| 4.2  | List of vector flag registers                           | 0 |

| 4.3  | List of control registers                               | 0 |

| 4.4  | Instruction qualifiers for opcode op                    | 1 |

| 4.5  | Vector arithmetic instructions                          | 2 |

| 4.6  | Vector logical instructions                             | 3 |

| 4.7  | Move instructions                                       | 3 |

| 4.8  | Vector flag processing instructions 33                  | 3 |

| 4.9  | Memory instructions                                     | 4 |

| 4.10 | Vector processing instructions                          | 4 |

| 5.1  | Load Store Instructions' Slope and Y-intercept 4        | 7 |

| 5.2  | VMUL and VADD instructions' slope and y-intercept 4     | 7 |

| 5.3  | VESHIFT and VMAC instructions' slope and y-intercept 50 | 0 |

| 5.4  | VFAND instructions' slope and y-intercept               | 1 |

| 5.5  | Software vs hardware performance for all instructions   | 4 |

| 5.6  | Pure software vs pure hardware performance              | 8 |

# Listings

| 3.1  | Software invoking operation on hardware | 5 |

|------|-----------------------------------------|---|

| 3.2  | Hardware implementation in VHDL 28      | 5 |

| 4.1  | Few example library calls for FVP       | 7 |

| 4.2  | Matrix multiplication in C              | 8 |

| 4.3  | Matrix multiplication in Library Calls  | 8 |

| 4.4  | SAXPY in C                              | 9 |

| 4.5  | SAXPY in library calls                  | 9 |

| 4.6  | FIR filter in C                         | 0 |

| 4.7  | FIR filter in library Calls             | 1 |

| 4.8  | String comparison in C 42               | 2 |

| 4.9  | String comparison in library calls      | 2 |

| 4.10 | Compare and exchange in C               | 3 |

| 4.11 | Compare and exchange in library calls   | 3 |

## Acknowledgement

I would like to express my sincere gratitude to my advisor Prof. Duane Bailey for the continuous support of my undergraduate study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis.

Besides my advisor, I would like to thank my second reader: Prof. Tom Murtagh, and the entire Williams College Computer Science department for their encouragement, insightful comments, and hard questions.

### Abstract

Roughly a decade ago, computing performance hit a *power wall*. With this came the power consumption and heat dissipation concerns that have forced the semiconductor industry to radically change its course, shifting focus from performance to power efficiency. We believe that Field programmable gate arrays (FPGAs) play an important role in this new era. FPGAs combine the performance and power savings of specialized hardware while maintaining the flexibility of general purpose processors (GPPs). Most importantly, pairing an FPGAs with a GPP to support *partnered computation* can yield performance and energy efficiency improvements, and flexibility that neither device can achieve on their own. In this work, we show that a GPP tightly coupled to a sequential vector processor implemented on an FPGA, called *Faux Vector Processor* (FVP), can support efficient, general purpose, partnered computation.

### 1. Introduction

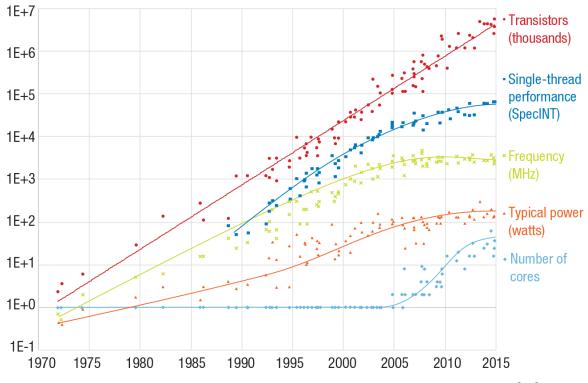

Microprocessor performance has increased dramatically over the past few decades. Until recently, Gordon E. Moore's famous observation that the number of transistors on *integrated circuits* ( $IC^1$ ) doubles roughly every 12-18 months (Moore's law) has continued unabated. The driving force behind Moore's law is the continuous improvement of the *complementary metal oxide semiconductor* (CMOS) transistor technology, the basic building block of digital electronic circuits. CMOS scaling has not only led to more transistors but also to faster devices (shorter delay times and accordingly higher frequencies) that consume less energy. During this period of growth, every generation of processor supported chips with twice as many transistors, executing of about 40% faster and consuming roughly the same total power as the previous generation [23]. The theory behind this technology scaling was formulated by Dennard et al. [7] and is known as *Dennard scaling*. There was a time when Dennard scaling accurately reflected what was happening in the semiconductor industry. Unfortunately, those times have passed.

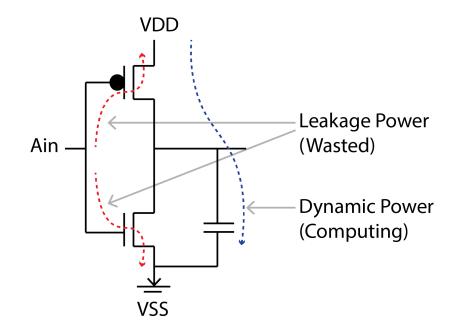

As the performance of processors improved due to shrinking transistors, the supply voltage of the transistors was not dropping at the same rate. As a direct consequence, chip power consumption grew with increased performance gains until only a decade ago. Higher power consumption results from current leakage, producing more heat. Power consumption and heat dissipation concerns have now forced the semiconductor industry to stop pushing clock frequencies further, effectively placing a tight limit on the total chip power. As a result, the frequency scaling driven by shrinking transistors has hit the so-called *power wall*. This trend is captured in Figure 1.1. In this new era, with each successive processor generation, the percentage of a chip that can switch at full frequency is dropping exponentially due to power constraints. Experiments conducted by Venkatesh et al. from UCSD show that we can switch fewer than 7% of transistors on a chip at full frequency while remaining under a power budget [27]. This percentage will decrease with each processor generation [27]. This underutilization of transistors due to power consumption constraints is called *dark silicon*.

$<sup>^1\</sup>mathrm{A}$  table of a cronyms can be found beginning on page 68.

Figure 1.1: 40 Years of trend in microprocessor data. Figure from Moore [23].

There are several approaches to building more power efficient architectures to tackle dark silicon. Traditionally engineers have achieved performance and energy improvements by using special purpose application specific integrated circuits (ASICs). ASICs are designed for a particular use. The biggest downside of dedicated ASICs is their inflexibility. Another promising way to overcome these limitations is to move towards heterogeneous architectures, where cores vary and tasks are off-loaded to specialized hardware. The specialized core will better at performing specialized computation and consume a lot less power. Effectively, enabling the hybrid architecture to stay under the power budget and utilize the silicon that would have dark. One way to build such hybrid architecture is to use a *general* purpose processor (GPP) with a set of tightly coupled ASIC co-processors. ASICs are designed for a particular use and are more efficient that GPPs as they do not need to include components for instruction decode. Graphic processors are an example of this approach. UCSD's *Conservation Core* project also demonstrated significant energy efficiency with this approach [27], but the approach inherits the inflexibility of ASIC-based design. The static nature of the ASIC cores makes it an impractical target when the codebase for the specific application changes. An alternative approach of building these heterogeneous architectures is to replace the ASIC like cores with reconfigurable cores. Reconfigurable cores provide

a compromise between GPPs and ASICs. *Field Programmable Gate Arrays* (FPGAs) are ideal candidates for the reconfigurable cores. While FPGAs are generally less computationally powerful than GPPs, they are more flexible than ASICs. Therefore, FPGA-based heterogeneous circuits consume moderate power, allow multiple specialized circuits to be "loaded" whenever they are needed, drastically reduce time-to-market, and also provide the ability to upgrade already deployed circuits. Of course, there is no free lunch: building heterogeneous architectures with FPGAs is a difficult and time-consuming process.

In this work, we explore the trade offs in designing a partnered computation pairing a GPP with a FPGA based vector processor. Unlike a typical vector processor, our vector processor will be optimized towards power efficiency rather than performance. Leading hardware manufactures are also starting to realize the possibility of FPGA based co-processors [11]. Intel, leading chip manufacture, recently announced that it is working to produce a GPP with a tightly coupled FPGA based processors. While FPGAs have made significant advances and are now highly capable, the software and documentation supporting them is still primitive. Therefore, in this work we also use the vector processor as a target architecture to take step closer towards mitigating the difficulties in programming FPGA to make it more accessible to programmers.

The rest of the chapters are organized as follows. Chapter 2 goes over the previous work on energy efficiency; comparison between GPPs, ASICs, and FPGAs; FPGA-based vector processors; heterogeneous co-processor systems; and power analysis on FPGA. Chapter 3 describes the traditional FPGA project workflow by walking through an example. In Chapter 4, we present the design and goals of our FPGA-based *faux vector processor* (FVP), followed by Chapter 5 that outlines our methodology for evaluating our design and describes our results. Chapter 6 suggests some options for future exploration. Finally, Chapter 7 briefly summarizes our findings.

## 2. Previous Work

Previous research related to this work can be grouped into four main categories. First, there is a large body of research focused on relative efficiency of computation performed on GPPs, FPGAs, and ASICs. Second, there has been significant work on improving the performance of conventional vector processors and also on designs that include vector processors as coprocessors. Third, there have been a number of attempts to design performance enhancing hardware designs. Finally, there is a small body of research focused on power analysis and optimization on FPGAs. We consider these contributions in this section.

#### 2.1 Efficiency Comparison Between GPPs, FPGAs, and ASICs

In this section, we'll look at previous works focused on the efficiency comparison between GPPs, FPGAs, and ASICs that informed our research on the benefits of using FPGA based cores.

Hill and Marty of University of Wisconsin extend Amdahl's simple software model and compute performance speedup for symmetric, asymmetric, and dynamic multicore chips [13]. Amdahl's software model is used to find the maximum expected improvement to an overall system when only part of the system is improved. Symmetric processors dedicate the same resources to each multicore (e.g. 16 identical 4-resource multicores on a 64-resource chip), asymmetric processors have differently sized cores (e.g. one 16-resource core and 24 2-resource cores), and dynamic processors can be run-time reconfigured to run as one powerful core for sequential processing or as a set of possibly asymmetric smaller cores for parallel processing. Even though multicore processors do not have application specific hardware, asymmetric multicores represent a similar approach to that of ASICs: trying to break up the larger computation into pieces that can be handled by optimally-sized sections of hardware. Their key conclusion is that in terms of performance, the dynamic multicore designs outperform asymmetric multicores, and asymmetric multicore designs perform better than symmetric ones. Similar to Hill and Marty's work, Woo and Lee of Georgia Institute of Technology extend Amdahl's law and develop analytical power models for symmetric, asymmetric, and dynamic chip design to evaluate energy efficiency on the basis of power models [29]. Their analysis demonstrates that symmetric and asymmetric multicore chips can easily lose their energy efficiency as the number of cores increases. Their work concludes that a dynamic multicore processor with many small energy efficient cores integrated with a single larger core provides the best energy efficiency.

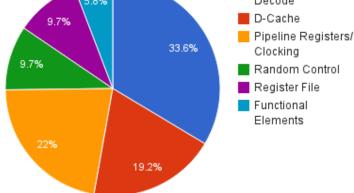

Hameed et al. analyze the inefficiencies of GPPs compared to ASICs [12]. According to their findings, GPPs spend over 90% of their computation on instruction fetch and decode and only 10% on computation as shown in Figure 2.1. Their results show that such overhead can be completely eliminated by using ASICs. ASICs are generally around  $50 \times$  more efficient than GPPs both in terms of power and performance because they can exploit parallelism, group complex instructions that are often used together, and make use of specialized hardware specifically designed for a target application. In this way, the authors claim that a truly efficient design will require application-specialized hardware.

mJ/Frame for Datapath in H.264

Figure 2.1: Chart of GPP computation energy. Roughly 5% of computation energy goes to the functional units, with most being spent on computational overhead. Data from Hameed et al. [12]

Kuon and Rose's work on measuring the performance and energy gap between FPGAs and ASICs describes the empirical measurements of the difference between a 90-nm CMOS FPGA and 90-nm standard-cell ASIC in terms of logic density, circuit speed and power consumption. Their results show that FPGA logic requires roughly  $35 \times$  more area (mostly due to routing),  $14 \times$  more power, and a 3-4× longer critical path. Most modern FPGAs have some hard logic blocks (arithmetic logic units (ALUs), random access memory (RAM) blocks, etc.), which can reduce those gaps to around  $18 \times$  for area, and  $8 \times$  for power with only minor impact on the delay, depending on how much of the application hardware can be mapped to those hard blocks. The cost of those improvements is the loss of flexibility on the FPGA, as fabric space must be dedicated to the hard blocks, whether or not they are used.

Chung et al. raise an interesting question in their work: "Does the future of chip design include custom logic, FPGAs, and General Purpose Graphic Processor Units (GPGPUs)?"[4]. They weigh the benefits and trade-offs associated with integrating unconventional cores (ucores) with GPPs to reach their conclusion that future chip design should include custom logic. Since power consumption and I/O bandwidth are the two main performance bottlenecks for modern computation, the authors evaluate three different types of u-cores, namely ASICs, FPGAs, and GPGPUs, paired with GPPs in terms of energy efficiency rather than pure performance. To accurately measure the energy efficiency, sequential operations are performed on the GPP and parallel operations are performed on the u-cores. Their results show that u-cores almost always improve the efficiency of computation, especially as the amount of parallelism in the target application increases. Further, the benefits of u-core use are heavily dependent on off-chip bandwidth trends. This is because bandwidth ceilings quickly become a limiting factor for extremely fast custom logic. Even if I/O and bandwidth improvements continue to lag behind logic improvements, FPGAs will be able to offer performance that is closer to that of ASICs than their relative computational efficiency would suggest. The authors conclude that ASICs offer both the highest performance and the most power efficiency, but that ASICs are expensive to develop and designed around a single set of target applications. On the other hand, FPGAs can provide significant efficiency gains over GPPs alone while offering more flexibility than ASICs.

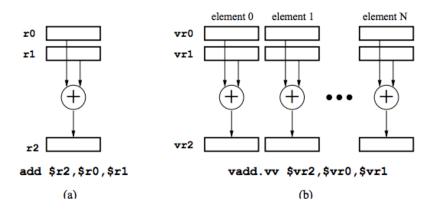

#### 2.2 The Return of the Vector Processor

A vector processor is a processor that can operate on an entire vector in one instruction. The operand to the instructions are complete vectors instead of single elements. Vector processors reduce the fetch and decode bandwidth as fewer instructions are fetched. They may also exploit data parallelism in applications. The difference between scalar and vector architecture is described in Figure 2.2. In this section, we describe the previous contributions that motivated our research to choose vector processors as the co-processor in our design.

In their 2002 paper, Kozyrakis and Patterson describe the Vector Intelligent RAM (VIRAM)

Figure 2.2: The difference between scalar and vector instructions. A scalar instruction (a) defines a single operation on a pair of scalar operands. An addition instruction reads two individual numbers and produces a single sum. On the other hand, a vector instruction (b) defines a set of identical operations on the elements of two linear arrays of numbers. A vector addition instruction reads two vector operands, performs element-wise addition, and produces a similar array of sums. Figure from Kozyrakis and Patterson [17]

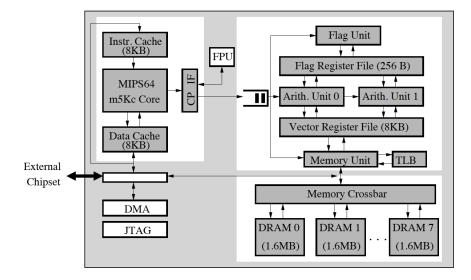

architecture aimed at developing a vector processor that provides high performance for multimedia tasks at low energy consumption [17]. The VIRAM micro-architecture relies on two basic technologies: vector processing and embedded DRAM. The vector architecture allows for high performance for multimedia applications by executing multiple element operations in parallel, and the embedded DRAM enables the integration of a large amount of DRAM memory on the same die with the processor. The vector hardware executes the VIRAM instruction set (a standard, straightforward extension of MIPS instruction set), connects to the scalar MIPS core as coprocessor, and operates at a modest speed of 200 MHz. The MIPS core supplies the vector instructions to the vector lanes for in-order execution, and vector load and store instructions access DRAM-based memory directly without using SRAM caches. The design partitions the register and data path resources in the vector coprocessor vertically into four lanes. Figure 2.3 shows the block diagram for the VIRAM architecture with its four components: the MIPS scalar core, the vector coprocessor, the embedded DRAM main memory, and the external IO interface. Overall, the authors are able to show that VIRAM architecture is more energy efficient and less complex than VLIW architecture and super scalar architecture. However, they claim that VIRAM is susceptible to the basic limitations of traditional vector designs: (1) the complexity and size of the centralized vector register file that limits the number of functional units, (2) the difficulty of implementing precise exceptions for vector instructions, and (3) the high cost of vector memory systems.

Figure 2.3: Figure showing the block diagram of VIRAM architecture. Figure from Kozyrakis and Patterson [17]

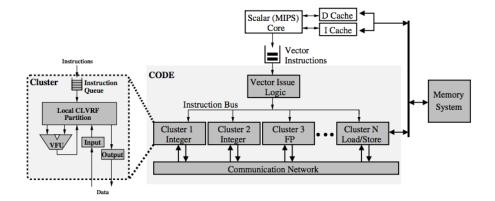

Figure 2.4: Figure showing the block diagram of CODE architecture. Figure from Kozyrakis and Patterson [18]

In their 2003 followup paper, Kozyrakis and Patterson attempt to address the limitations of VIRAM architecture by introducing an improved micro-architecture called Cluster organization for Decoupled Execution (CODE) [18]. CODE differs from the VIRAM microarchitecture in two ways. First, it breaks up the centralized register file and distributes the vector registers across all cores. Second, it uses decoupling, instead of the delayed pipeline, to tolerate long memory latencies. VIRAM structures the vector coprocessor around a cen-

tralized vector register file that provides operands to all functional units and connects them to each other. In contrast, the composite approach organizes vector hardware as a collection of interconnected cores. Each core is a simple vector processor with a set of local vector registers and one functional unit. Each core can execute only a subset of the instruction

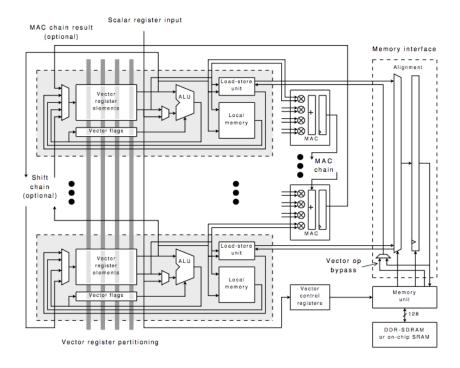

set. For example, one vector core may be able to execute all integer arithmetic instructions, while another core handles vector load and store operations. The composite organization breaks up the centralized vector register file into a distributed structure, and uses renaming logic to map the vector registers defined in the VIRAM architecture to the distributed register file. The composite organization uses a communication network for communication and data exchange between vector cores, as there is no centralized register file to provide the functionality of an all-to-all crossbar for vector operands. The block diagram of CODE is shown in Figure 2.4. Their results show that CODE is 26% faster than a VIRAM with a centralized vector register file that occupies approximately the same die area. They are also able to show that CODE only suffers less than 5% performance loss due to precise exception support. Most importantly, CODE is able to scale the vector coprocessor in a flexible manner by mixing the proper number and type of vector cores. If the typical workload for a specific implementation includes a large number of integer operations, more vector cores for integer instruction execution could be allocated. Similarly, if floating-point operations are not necessary, all cores for floating-point instructions could be removed. In contrast, with VIRAM one could only increase performance by allocating extra lanes, which evenly scales integer and floating-point capabilities, regardless of the specific needs of applications. Yu et al. demonstrate the potential for vector processing as a simple-to-use and salable accelerator for soft processors [34]. Their architecture consists of a scalar core (single threaded version of 32-bit Nios II), a vector processing unit, and a memory unit. The scalar core and the vector unit share the same instruction memory and the same instruction fetch logic. The scalar and vector units can execute instructions in parallel and also can coordinate via a FIFO queue for instructions requiring both cores. The vector unit is a VIRAM based vector architecture extended to take advantage of on chip memory blocks and hardware multiply accumulate (MAC) units common in FPGAs. The vector unit is composed of a specified number of vector lanes, each with complete copies of a functional unit, partition of the vector register file and vector flag registers, load store unit, and local memory. Through performance modeling the authors are able to show that a vector processor can potentially accelerate data parallel benchmarks with performance scaling better than Altera's behavioral synthesis tool even after manual code restructuring. Further, they are also able to show how FPGA architectural features can be exploited to provide efficient support for some vector operations. For example, the multiply-accumulate blocks internally sum multiple partial products from narrow multiplier circuits to implement wider multiplication operations. Figure 2.5 shows the block diagram of vector component of their soft core architecture.

Figure 2.5: Figure showing the block diagram of vector coprocessor in soft core processor architecture. Figure from Yu et al. [34]

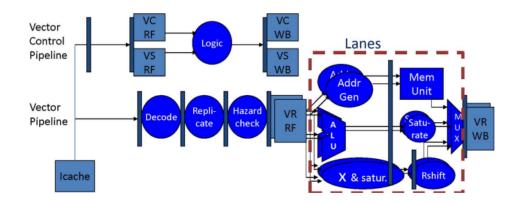

Yiannacouras et al. extend this work by proposing a full and verified hardware implementation of a soft vector processor called Vector Extended Soft Processor Architecture (VESPA), connected to off-chip memory, and with GNU assembler vector support [32]. VESPA is a MIPS-based scalar processor with a highly configurable VIRAM-like vector coprocessor implemented using Stratix III FPGA. The scalar and the vector coprocessors share the same instruction cache, and both cores can execute out-of-order with respect to each other except for communication and memory instructions which are serialized to maintain sequential memory consistency. VESPA architecture is composed of three pipelines. Figure 2.6 shows the VESPA pipelines with each stage separated by black vertical bars. The topmost pipeline is the three-stage scalar MIPS processor discussed earlier. The middle pipeline is a simple three-stage pipeline for accessing vector control registers and communicating between the scalar processor and vector coprocessor. The actual vector instructions are executed in the longer seven-stage pipeline at the bottom of Figure 2.6. Vector instructions are first decoded and proceed to the replicate pipeline stage which divides the elements of work requested by the vector instruction into smaller groups that are mapped onto the available lanes. VESPA is also a highly configurable design as all parameters are built-in to the Verilog design so a user need only enter the parameter value and have the correct configuration synthesized with no additional source modifications. With VESPA, Yiannacouras et al. are not only able to show that their architecture can scale performance from  $1.8 \times$  up to  $6.3 \times$ , but also automatically generate application-specific vector processors with reduced datapath width and instructions set support which combined reduce the area by 70% without affecting performance.

Figure 2.6: VESPA architecture with two lanes. The black vertical bars indicate pipeline stages, the darker blocks indicate logic, and the light boxes indicate storage elements for the caches as well as the vector control (vc), vector scalar (vs), and vector (vr) register files. Figure from Yiannacouras et al. [32]

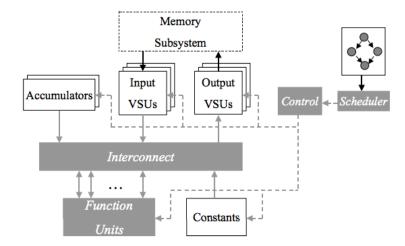

Ciricescu et al. describe a vector coprocessor accelerator architecture called the Reconfigurable Streaming Vector Processor (RSVP) that improves the performance of streaming data. RSVP uses a stream oriented approach to vector processing by decoupling and overlapping data access and data processing. There are several load/store units that prefetch vector data from long-latency, wide memory and turn it into narrow, high speed streams of vector elements, that communicate with the processing units via an interlocked FIFO queue. RSVP uses a programming model that separates data from computation; data is described by location and shape in the memory and computation is described using machine independent data flow graphs. Figure 2.7 shows the block diagram of vector component of their soft core architecture. The white components are visible to the programmer while the grey components represent data-flow computation structure that is hidden from the programmer. Overall, the authors are able to show that RSVP achieves speedups for kernels and applications range from 2 to over  $20 \times$  that of a host processor alone, and is easy to

market because of the ease of programmability.

Figure 2.7: The RSVP Architecture. Figure from Ciricescu et al. [5]

#### 2.3 Performance- and Power-Improving Designs

In this section, we look at specialized hardware designed for performance and energy efficiency. The architectures discussed in this section are hybrid systems with a GPP tightly coupled with one or more co-processing units. The architectural choices described in these contributions have motivated important design decisions in our design.

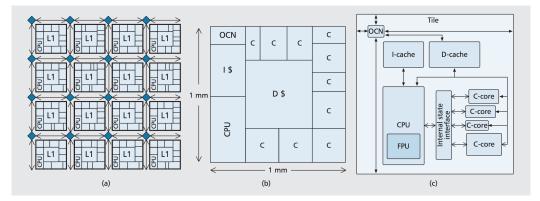

In 2010, Venkatesh et al. from UCSD analyzed the benefits of pairing specialized conservation cores (c-cores) with GPPs with the aim of significantly reducing the power consumption for frequently executed, energy intensive code [27]. As described in Chapter 1, the frequency-scaling power wall has made energy efficiency, rather than pure computational speed, the primary bottleneck. They argue that if a given computation can be made to consume less power at the same level of performance, then other computations can be run in parallel without violating the power budget. As a result, their primary focus is not increased performance, but rather similar performance with lower energy consumption. Because they target energy efficiency, rather than computation speed, c-cores can be used for a much broader set of applications or code blocks, even when there is no available parallelism to exploit. Even when there is not parallelism to be exploited (or when acceleration via increased parallelism is not the goal), using c-cores simply to make computation more energy efficient is worthwhile because it allows more of the chip to be functional at any given time. The c-core system, as described, contains multiple tiles, each of which contains one GPP and several heterogeneous c-cores as shown in Figure 2.8. The researchers' toolchain generates c-cores by profiling a target workload, selecting "hot" code regions, and automatically synthesizing c-core hardware to implement the code block. The compiler must be extended to use available c-cores on applicable code segments, while executing other code on the GPP. The researchers also discuss "patchable" c-cores, which are more flexible (increasing their lifetime and the amount of code they can execute) but incur  $2\times$  area and power consumption overhead. Their results suggest that a system using 18 c-cores can have a  $16\times$  improvement in energy consumption for code that can be executed on the c-cores, resulting in a reduction of nearly 50% for the energy consumption of the target applications as a whole.

Figure 2.8: A diagram showing (a) a c-core chip with multiple tiles, (b) the physical floorplan for an individual tile, and (c) the logical layout of the interconnects within a tile. Figure from Goulding-Hotta et al. [10]

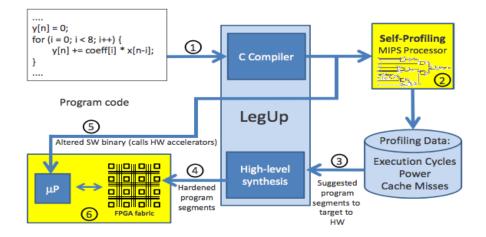

Canis et al. present an open source, high-level synthesis tool called LegUp that leverages software techniques for hardware design[3, 2]. Their design allows users to explore the hardware/software design space. Using the architecture some portion of a program can run on a GPP, and others can be implemented as custom hardware circuits. LegUp takes a standard C program as an input and automatically compiles the program to a hybrid architecture containing a FPGA-based MIPS soft processor and custom hardware accelerators that communicate through a standard bus interface. Their design flow comprises first compiling and running a program on a standard processor, profiling its execution, and then recompiling the program to a hybrid hardware/software system. In their design, they leverage the LLVM compiler framework for high-level language parsing and its standard compiler optimization [20]. Figure 2.9 shows the detailed design flow for LegUp. Their architecture can synthesize most of the C language to hardware, like fixed-sized multi-dimensional arrays, structs, global variables and pointer arithmetic. However, dynamic memory, floating point, and recursion is not supported by their architecture. Overall, compared to software running on

Figure 2.9: The Block diagram showing LegUp design. Figure from Canis et al. [2]

a MIPS soft processor, hybrid architecture provided by LegUp execute  $8 \times$  faster and use  $18 \times$  less energy.

#### 2.4 GPP-FPGA Communication

While FPGA technology seems so promising, we can not fully realize the potential of FPGA-GPP architecture without having some form of interface between the logic fabric and the computer program running on the GPP. In this section, we look at some of the contributions made in this field.

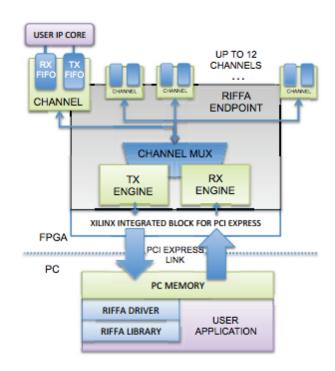

Jacobsen and Kastner from UCSD designed a reusable integration framework for FPGA accelerators called Reusable Integration Framework for FPGA Accelerators (RIFFA) [14]. RIFFA is a simple framework for communicating data from a host CPU to a FPGA via a PCI express bus. RIFFA is an alternative to Xillybus, which is used in our project. The framework requires a PCI eenabled workstation and a FPGA on a board with a PCI connector. RIFFA supports Windows and Linux, Altera and Xilinx, with bindings for C/C++, Python, MATLAB and Java. On the software side there are two main functions: data send and data receive. These functions are exposed via user libraries in C/C++, Python, MATLAB, and Java. The driver supports multiple FPGAs (up to 5) per system. The software bindings work on Linux and Windows operating systems. On the hardware side, users access an interface with independent transmit and receive signals. The signals provide transaction handshaking and a first word fall through FIFO interface for reading/writing data. No knowledge of bus addresses, buffer sizes, or PCIe packet formats is required. RIFFA

does not rely on a PCIe bridge and therefore is not subject to the limitations of a bridge implementation. Instead, RIFFA works directly with the PCIe endpoint and can run fast enough to saturate the PCIe link. Their experiments show that RIFFA can achieve 80% of the theoretical bandwidth of data transfer between host CPU and FPGA over PCI bus in nearly all cases. Figure 2.10 shows the block diagram of the RIFFA architecture. The downside in their architecture is that the details of PCIe protocol device driver, DMA operation, and all hardware addressing are hidden from the software and hardware in their architecture. As a result some user flexibility is lost because of the design choice.

Figure 2.10: RIFFA 2.0 architecture. Figure from Jacobsen and Kastner [14]

Similar to RIFFA, Connectal by King et al. from Quanta Research Cambridge is a software driven hardware development framework which aims to narrow the boundary between the software and hardware development using FPGA [16]. Their hardware components are written in Bluespec System Verilog (BSV) and the software components are implemented in C/C++. Using BSV, their architecture allows users to declare logical groups of unidirectional "send" methods, each of which is implemented as a FIFO channel; all channels corresponding to a single BSV interface are grouped together into a single "portal". The hardware and software communicate with each other using these portals. Overall, their framework connects software and hardware by compiling interface declaration, allows concurrent access to hardware accelerators from software, allows high-bandwidth sharing of system memory with the hardware accelerators, and also provides portability across different platforms.

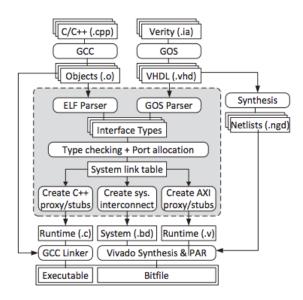

In 2015, Fleming et al. from Imperial College of London, present a system-level linker called PushPush, which allows functions in hardware and software to be linked together to create heterogeneous systems [8, 25]. PushPush links together pre-compiled modules from different compute domains and languages, called "system objects". System objects are modules which export a set of functions and also may import functions from others. They can be software functions, classes, libraries, or intellectual property (IP) cores in hardware. Design flow of their architecture is shown in Figure 2.11.

Figure 2.11: Design flow diagram for PushPush linker. Figure from Fleming et al. [8]

The system linker is shown in gray and it takes in software and hardware object files to be linked as input. At the next step, the type information is parsed out of the binary files using ELF information in the software binary or Verity's equivalent meta-data. All function names and types are then merged and similar checks as that of software linker (eg type checking) are performed. All symbols are resolved to one exporter and zero or more importers. At the next stage, proxies and stubs are added on both hardware and software sides, and linking code is generated that connects imported symbols in one module to exported symbols in another. In the final stage, all the components are combined. The software side is linked together with the standard linker bringing together the user's software and the system linker's proxies and stubs. For hardware, the system linker generates an IP block incorporating the CPU, user's hardware, and the Advanced eXtensible Interface (AXI) proxies and stubs. The final result is a single executable containing both software and hardware. The researchers also built a fully functional and automated prototype on the Zynq platform and are able to show that this type of linking enables a more equal partnership between hardware and software, with hardware not just acting like a "dumb accelerator" but also being able to initiate execution across the system.

#### 2.5 Power Consumption Analysis on FPGA

Analysis and estimation for power dissipation of FPGAs has received little attention compared to that of standard cell ASIC. Most of this limited research on FPGA power consumption have focused primarily on dynamic power consumption. There has been very little work to estimate and analyze static power consumption of FPGAs. In this section, we discuss some of the work done towards analyzing both dynamic and static power consumption on an FPGA. These contributions will serve as a reference for power analysis of our design in later chapters.

Tuan and Lai from Xilinx Research Lab and UCLA analyze the leakage power of a low-cost 90nm FPGA using detailed device-level simulation. There simulations are performed using DC operating point analysis in SPICE. DC operating point analysis calculates the behavior of a circuit when a DC voltage or current is applied to it. The result of this analysis is generally referred as the bias point, quiescent point or Q-point. The author's measurement methodology is based on measuring the power consumption by configurable logic blocks (CLBs), building block of the FPGA circuit. The authors first divide the CLBs into smaller circuit blocks. Next, each block is simulated individually to identify its leakage power consumption. As the FPGA architecture is highly regular, iterating over all the circuit blocks is quite manageable. The total leakage power of the CLB array is then computed by taking the sum of each block's leakage power. Finally, this total power consumed by CLB array is multiplied by the number of CLBs in the array to get the total leakage power. To model the effect of input variation, the simulation is performed under all possible input states of circuit blocks. Using this methodology, they found that their FPGA consumes  $4.2\mu W$  static power per CLB under normal conditions and more than  $26\mu W$  per CLB in the worst case. The authors conclude that there is a potential for substantial leakage reduction through optimization of basic circuits and power management based on resource utilization.

Shang et al. from Princeton University and Xilinx Research Lab analyze the dynamic power consumption in an FPGA by taking advantage of both simulation and measurement. The target device for this project is a Xilinx Virtex-II. According to the authors, the total power dissipation is a function of three factors. First is the effective capacitance, which is defined as the "parasitic" effect due to interconnection wires and transistors, and the emulated capacitance because of short-circuit current. The effective capicatance of each resource is computed using direct measurement and SPICE simulation. The second factor is the resource utilization, i.e the proportion of look up tables (LUTs), block RAMs (BRAMs) etc used in circuit design. Finally, the most important factor determining the power dissipation is the switching activity. Switching activity is defined as the number of signal transitions in a clock period. Resource utilization and switching activity is computed using software called Modelsim. The authors model these factors as follows

$$P = \frac{1}{2}V^2 f \sum_i C_i U_i S_i$$

where V is the supply voltage, f is the operating frequency, and  $C_i, U_i, S_i$  are the effective capacitance, utilization, and switching activity of each resource, respectively. Using this equation, the authors compute the power dissipation of few benchmark circuits. According to their results most of the power dissipation occurs in the interconnection resources. The authors also conclude that for the xilinx Vertex-II FPGA operating at 100MHz with input voltage of 1.5V, each CLB would consume  $5.9\mu$ W per MHz.

There has been considerable work on dynamic power analysis on FPGAs. Degalahal and Tuan model dynamic power consumption of FPGA based on clock power, switching activity, and dominant interconnect capacitance. Similarly, Jevtic and Carreras present a measurement model that separately measures clock, interconnect, and logic power to compute the total dynamic power consumed by the FPGA. These are some direct ways of measuring power consumption on an FPGA. An alternative to this approach is to rely on power analysis software to measure the power consumption. For the purpose of this project, we relied on Vivado's power analysis tool to measure the power consumption of our design, and are aware that better estimates are possible.

#### 2.6 Summary

The computational performance of a chip has hit a power wall [27]. As a result, it is becoming increasingly difficult to improve energy efficiency while maintaining computational performance. A lot of work has been done to evaluate the performance and energy efficiency of ASICs, FPGAs, and GPPs to determine the right architecture for the job. The past works comparing different kinds of heterogeneous processors have shown that even though ASICs have a considerable performance advantage compared to FPGAs, FP-GAs can be significantly more efficient than general purpose processors while maintaining enough flexibility to be used for a wide variety of applications. Furthermore, designs that combine heterogeneous accelerators with GPPs make it clear that such a design can offer significant flexibility with performance and efficiency gains compared to a GPP, ASIC, or FPGA alone. The c-core and QS-core research [27, 28] suggests that a system integrating automatically generated ASICs with a modified compiler and runtime controller can significantly reduce power consumption. Similarly, the RIFFA, PushPush, and Connectal research [3, 8, 16] have shown that a system integrating FPGA with a modified runtime controller can significantly improve power and performance efficiency. These efforts have focused on trading execution of instruction for hardware, and mostly neglect the possibility to harness the power of parallelism. Previous works on vector processors have shown the possibility to solve the problem through parallelism. The projects like VIRAM, VESPA, CODE, RSVP [17, 18, 32, 5] have made it clear that vectors processors can be very efficient co-processors and can provide significant performance and energy boost. Works described in this section suggests that a heterogeneous design with a GPP tightly coupled with one or many reconfigurable co-processors would yield significant energy efficiency gains while maintaining flexibility.

## 3. The FPGA Work Flow

Since FPGAs provide a compromise between the performance of ASICs and the flexibility of GPPs, the FPGA seems an ideal partner for a GPP. The Xilinx Zynq-7000 is one such heterogeneous computing platform used in this project. It integrates a dual-core Cortex A9 ARM processor and an FPGA inside one chip. Moreover, because of its tightly-coupled processing system (PS) and programmable logic (PL), the Xilinx's Zynq seems to be an ideal platform on which to implement a configurable co-processor. Figure 3.1 shows a picture the Xilinx's Zynq-7000 ZedBoard Evaluation Kit. Before we consider our proposed architecture, we describe the architecture of an FPGA, typical workflow for programming an FPGA, and the pros-and-cons of the tools encountered.

Figure 3.1: Xillnx's Zedboard. Figure from Zedboard's Website[35]

#### 3.1 Field Programmable Gate Array Architecture

In this section, we give an overview of the technology behind field programmable gate arrays (FPGAs). FPGAs arose from programmable logic devices (PLDs), which first appeared in early 1970s. However, these early FPGAs were very limited as programmable logic was hardwired between logic gates. In 1985, the first commercially available FPGA (the Xilinx XC2064) hosted arrays of *configurable logic blocks* (CLBs) that contained *programmable gates* as well as *programmable interconnect* between the CLBs. Since then FPGAs have rapidly evolved.

Now, most FPGAs are composed of three fundamental components: combinational logic (compute), memory elements (storage), and a programmable interconnect (communication). In custom ASIC, combinational logic is built by wiring a number of physical basic logic gates together. In FPGAs, these logic gates are simulated using multiple instances of a generic configurable element called a *look-up-table* (LUT). An n-input LUT can be used to implement an arbitrary deterministic function with up to n inputs. Each LUT is paired with a flip-flop (FF). This facilitates pipelined circuit design, where signals may propagate through large part of the FPGA chip. LUTs can also be configured to support, in parts, as *distributed RAM* (Memory LUTs in Xilinx architecture).

A fixed number of LUTs are grouped and embedded into a programmable logic component called *elementary logic unit*. Xilinx refers these units as *slices* in their architecture. The exact architecture of elementary logic units varies among different vendors and even between different generations of FPGAs from the same vendor. Nevertheless, we can identify four main structural elements: LUTs (usually between two to eight), registers, arithmetic/carry logic, and multiplexers. A small number of these elementary logic units are grouped together into a coarser grained *logic island*, or configurable logic block (CLB).

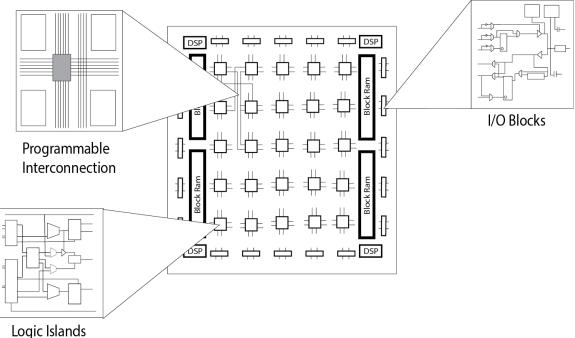

The *interconnect* is a configurable routing architecture that allows communication between arbitrary logic islands. It consists of communication channels (bundles of wires) that run horizontally and vertically across the chip, forming a Manhattan-style grid. Where routing channels intersect, *programmable links* determine how signals are routed. As illustrated in Figure 3.2, the two-dimensional array of communication logic islands is surrounded by I/O blocks (IOBs). These IOBs, at the periphery of the FPGA, connect the programmable interconnect to the adjacent circuitry.

The logic resources of FPGAs discussed so far are, in principle, sufficient to implement a

wide range of circuits. However, to address high performance and usability needs, FPGA vendors additionally intersperse FPGAs with special silicon components such as *block RAMs* (BRAMs) and *digital signal processors* (DSP units). BRAMs can hold comparatively large amount of data making them ideal choice to store large amount of working data on-chip. DSP units contain dedicated hardware to support arithmetic signal processing, including high performance multipliers and adders. These are a few examples of embedded silicon components on FPGAs. Often FPGA vendors add more complex hardwired circuitry to their FPGAs to support common functionality at high performance with minimal chip space and power consumption. Having discussed the key components of FPGAs, we now consider how FPGAs are programmed.

.ogic Islands

Figure 3.2: Block diagram showing FPGA layout.

#### 3.2 Architecture Supporting Partnered Communication

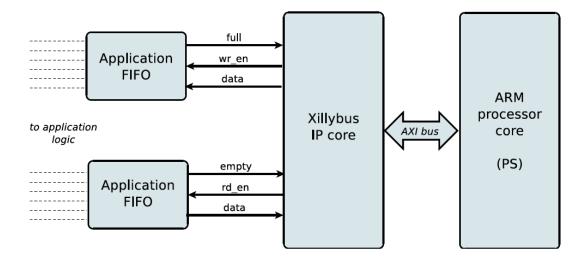

One of the daunting tasks in FPGA design is effectively communicate with adjacent processors. Implementing the low-level bus protocols is a project in itself. In this work, we used a pre-packaged communication solution, Xillybus, to allow us to focus our efforts on co-processor design.

Xillybus consists of an IP core and a Linux driver. IP cores are the FPGA equivalent of library functions. IP cores may implement certain mathematical functions, a functional unit (example, a USB interface), an entire processor (e.g. ARM). They promote hardware design reuse. Managed by linux driver, Xillybus forms a kit for elementary data transport between an FPGA and the host, providing pipe-like data streams with a relatively straightforward user interface. It is intended as a low-effort solution for mixed partnered computations like ours, where it makes sense to have the project-specific part of the driver running as a user-space process. On the host side, the FPGA looks like a character device file. On the FPGA side, hardware FIFOs are used to control the data stream. Figure 3.3 shows how the FPGA interacts with the ARM processor. The Xillybus core on the Zynq operates at 100 MHz.

Figure 3.3: Xillybus overview[31]

#### 3.3 FPGA reconfiguration workflow

To demonstrate the considerations encountered in the typical FPGA workflow, we walk through the implementation of a typical application: computation of the dot product of two vectors.

#### 3.3.1 Typical Application: Dot Product of Vectors

Dot product (or scalar product) is an operation that takes two equal-length vector of numbers and returns a single number. Algebraically, it is defined as the sum of the product of the corresponding entries of the two sequences of numbers (Algorithm 1). Geometrically, it is the length of one vector projected on the other. Dot product, important in many scientific applications, is a good candidate for hardware acceleration.

#### Algorithm 1 Dot Product

**Require:** Input n > 0, A and B non empty

1:  $i \leftarrow 0$ 2:  $result \leftarrow 0$ 3: while i < n do4:  $result \leftarrow result + A[i] \times B[i]$ 5:  $i \leftarrow i + 1$ 6: end while 7: return result

#### 3.3.2 Describing the Circuit

The first step towards using the Zynq PL is describing a circuit that will compute the target function. Xilinx supports the two most common *hardware description languages* (HDL), Verilog and VHDL. We chose to use VHDL for this project. Even though VHDL code may look similar to code from traditional software programming languages, there are important difference. VHDL is a parallel dataflow language, unlike sequential computing languages such as C and assembly code. While sequential language instructions must be interpreted by the CPU, VHDL code creates a defination file for an inherently parallel circuit that can be realized directly as a circuit or indirectly as an FPGA hardware.

```

int dot_product(int* A, int* B, int size){

1

2

3

int result;

4

int i = 0;

5

6

for(i = 0; i < size; i++){</pre>

7

8

//pass A[i] and B[i] to the PL

9

pass_args_to_PL(A[i],B[i],size);

10

11

//synchronize data communication

12

//and wait for the computation to complete

13

synchronize_and_wait();

}

14

15

16

//retrieved the result

17

retrieve_result(result);

18

19

return result;

20 }

```

Listing 3.1: Software invoking operation on hardware

```

1 -- arguments are stored as local signals

2 signal val1: std_logic_vector(31 Downto 0) := get_first_argument();

3 signal val2: std_logic_vector(31 Downto 0) := get_second_argument();

4 signal size: integer := to_integer(unsigned(get_third_argument()));

5

6 signal result: std_logic_vector(31 Downto 0);

7 signal count : integer := 0;

8 signal state : integer := computing;

9

10 -- perform computation every clock cycle

11 signal temp_data: std_logic_vector(31 Downto 0);

12 case state is

13

when computing =>

14

if (count /= size) then

15

temp_data <= multiply(val1, val2);</pre>

16

17

result <= result + temp_data;</pre>

18

state <= computing;</pre>

19

count <= count + 1;</pre>

20

21

--signal computation performed; synchronize

22

computation_performed();

23

else

24

state <= done;</pre>

25

end if;

when done =>

26

27

transfer_result_back(result);

28

state <= complete;</pre>

29

end case;

```

Listing 3.2: Hardware implementation in VHDL

To show how to perform dot product of vectors using this software-hardware hybrid architecture, we implemented Algorithm 1 in C and VHDL. These two implementations are shown in Listings 3.1 and 3.2, respectively.

The computation is initiated in the processing system (PS), with software passing required values to the hardware. The software then waits. Once the programmable logic (PL) gets the required values, the computation starts. Computation happens every clock cycle. Since the clocks are running at different speed on PS and PL, two computing partners must be synchronized. This process repeats until all the entries of the vectors have been consumed. The PL then sends the result back to the software, and the computation is complete.

#### 3.3.3 Simulation

Figure 3.4: Implemented circuit diagram

Since producing a hardware circuit is a lengthy process, *simulation* is a crucial tool for designing any hardware efficiently in an FPGA. Testing a VHDL circuit is significantly more complex than testing a software application. There are various level of granularity at which a circuit can be simulated (eg, high level behavioral correctness to estimating propagation delays) and a VHDL *testbench* created for simulation must accurately mimic the hardware environment. Instead of simply calling a function with few different test inputs, a designer must define and provide a clocking mechanism and interfaces between the circuit being tested and the testing unit.

The next step is inserting any new *intellectual property* (IP) blocks. To use the newly created IP core, it must be interconnected with other hardware, which effectively lays out a floor plan. This involves importing other Xilinx IPs, including the IP for the ARM PS, and connecting the different pieces of IP correctly.

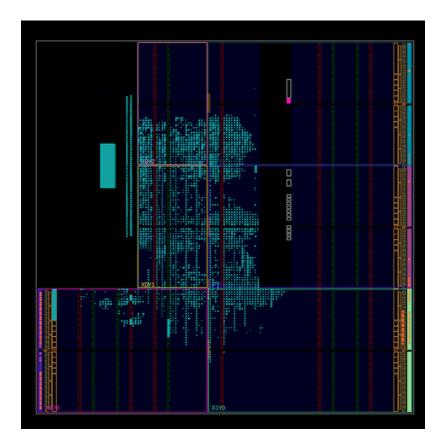

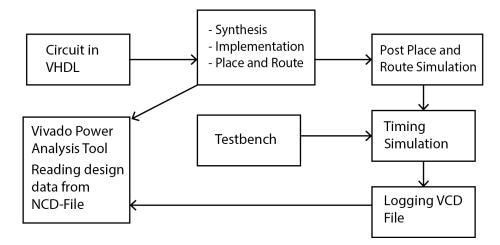

#### 3.3.4 Synthesis and Implementation

Once the block diagram is complete and all interconnects have been managed correctly, it is synthesized and implemented. Unlike software compilation, which usually takes a few seconds, Vivado's synthesis generally take a few minutes to run. This makes turnaround time to updating an IP core extremely time consuming, as even minor changes require a significant amount of time to implement. Synthesis and implementation output many reports, some of which detail the resource utilization of the IP cores, and predicted power consumption by the implemented circuit. A picture of hardware implementation of the design is shown in Figure 3.4. Finally, bitstream is generated for the implemented design. The bitstream file augments the system boot file and is loaded by the first stage boot loader to initialize the FPGA before the processor is booted. Once installed, the hardware is available through Xillybus device file.

#### 3.4 Summary

Even though Zynq is a great system to build a tightly-coupled coprocessor for a GPP, the process of programing the system is very much involved. We believe that complexity of this process represents a significant "barrier-to-entry" for new applications. This is unfortunate, given the great potential of these systems. In the next chapter, we describe an IP core that, at a high level, can be reconfigured or reprogrammed very easily. We believe this approach of targeting a reconfigurable one-time-programmed co-processor represents a happy medium between dedicated ASIC design and user-driven FPGA design as it combines the flexibility and efficiency of both.

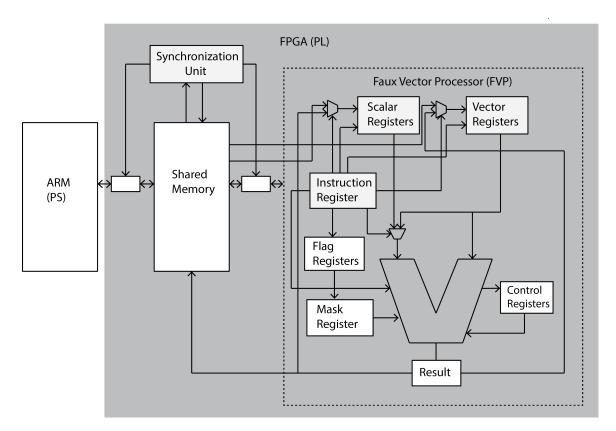

## 4. Faux-Vector Processor

In-spite of the complex programming model, the concept and benefits of an FPGA-based co-processor is very promising as it combines favourable characteristics of GPP and ASIC designs. In this section, we propose a FPGA-based vector reconfigurable co-processor. Along with the design and implementation details of the co-processor, we also provide some example applications that make use of the co-processor.

Previous research suggests that FPGA-based co-processors can provide significant performance improvement over a GPP alone. However, FPGA flexibility and efficiency comes at a significant workflow-cost. The devices are complex (Zynq's 1863 page manual [30]); the learning curve for VHDL is steep; and the configuration tool is buggy and poorly documented. Still, FPGAs remain popular devices supporting soft processors used in embedded systems. Soft processors are HDL-specified processors that can be configured in various ways supporting varying performance and resource utilization. The key benefit of using FPGAs for soft processors is that they can achieve high performance with reduced development effort to the user once they are designed. As a primary goal to this work, we have designed a soft vector processor called the Faux-Vector Processor (FVP).

In this new power-conscious era, efforts like the Conservation Core project from UCSD [27] have demonstrated a new way of designing power-efficient chips by configuring the excess transistors on the chip as power efficient hardware for specific application. In this work, we replace ASIC-like static core with a FPGA-based reconfigurable core, the FVP. This vector processor is optimized for power efficiency rather than speed. In a traditional GPP, a significant percent of power consumption comes from interpreting instructions. Vector processors perform entire loops as a single instruction so they can significantly reduce the power associated with instruction interpretation. We leverage this aspect of vector processor design to implement a single lane vector processor to realize the potential of performing computation with less overall power. The single lane vector processor executes operations sequentially rather than in parallel, hence the name *Faux* Vector Processor.

## 4.1 FVP Architectural Overview

The FVP is a single-instruction-multiple-data (SIMD) array of virtual processors (VPs) embedded on a Zynq processor. The number of VPs is the same as the vector length (VL). All VPs execute the same operation specified by a single vector instruction. The instruction set in this architecture borrows heavily from the VIRAM instruction set [21], which is designed as a vector extension to the MIPS-IV instruction set. A few instructions are borrowed from VESPA's ISA [33]. Operations however are performed sequentially rather than in parallel; the processor's focus is the development of power-efficiency without reduction of performance.

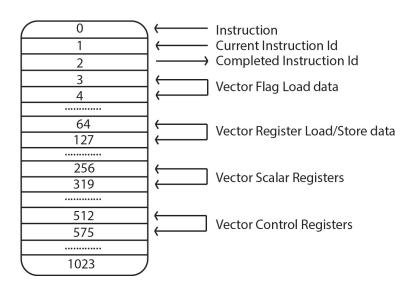

#### 4.1.1 Interface

NLane and MVL are fixed for the processor. They control the number of parallel vector lanes and functional units that are logically available in the processor, and the maximum length of the vectors that can be stored in the processor's vector register file, respectively. VPW and MemMinWidth control the data width of the VPs, and the minimum data width that can be accessed by vector memory instructions, respectively. Table 4.1 shows the list of parameters for the processor, their descriptions, and possible values.

| Table 4.1: | List of | parameters | for th | ne Faux | Vector | Processor |  |

|------------|---------|------------|--------|---------|--------|-----------|--|

|            |         |            |        |         |        |           |  |

| Parameter   | Description                             | Range of values | Type     |    |

|-------------|-----------------------------------------|-----------------|----------|----|

| NLane       | Number of lanes                         | 1               | Fixed    |    |

| MVL         | Maxumum vector length                   | 64              | Fixed    |    |

| VPW         | Processor data width (in bits)          | 8,16,32         | Variable |    |

| VL          | Vector Length                           | 1-64            | Variable |    |

| MemWidth    | Memory interface width (bits)           | 32,64           | Variable |    |

| MemMinWidth | Minimum accessible data width in memory | 8,16,32         | Variable |    |

|             |                                         |                 |          | i. |

The architecture defines sixty-four vector registers, and thirty-two 32-bit scalar registers. Vector-scalar instructions and certain memory operations require vector register and scalar register operands. Scalar register values can be transferred to and from vector registers or vector control registers using the vext, vins, vmstc, vmcts instructions.

Further, the architecture defines thirty-two vector flag registers. The flag registers are written to by comparison instructions and are operated on by flag logical instructions. The

| Hardware Name | Software Name | Contents        |

|---------------|---------------|-----------------|

| \$vf0         | vfmask0       | Primary mask    |

| \$vf1         | vfmask1       | Secondary mask  |

| \$vf2         | VF0           | General purpose |

|               |               |                 |

| \$vf31        | VF29          | General purpose |

Table 4.2: List of vector flag registers

vector masks are stored in the first two vector flag registers. Almost all instructions in the instruction set support conditional execution using a vector mask, specified by a mask bit. Table 4.2 shows a complete list of flag registers.

The architecture also defines sixty-four control registers. These registers are responsible for controlling the communication of important information between the host and the coprocessor. Table 4.3 shows a complete list of control registers and their use.

| Hardware Name | Software Name | Contents                                           |

|---------------|---------------|----------------------------------------------------|

| \$vc0         | VL            | Vector length                                      |

| \$vc1         | VPW           | Virtual processor width                            |

| \$vc2         | VINDEX        | Element index for insert (vins) and extract (vext) |

| \$vc32        | vstride0      | Stride register 0                                  |

|               |               |                                                    |

| \$vc39        | vstride7      | Stride register 7                                  |

| \$vc40        | vinc0         | Auto-increment Register 0                          |

|               |               |                                                    |

| \$vc47        | vinc7         | Auto-increment Register 7                          |

| \$vc48        | vbase0        | Base register 0                                    |

|               |               |                                                    |

| \$vc63        | vbase7        | Base register 7                                    |

Table 4.3: List of control registers

### 4.1.2 Instruction Set Architecture

The following section describes, in detail, the instruction set of the FVP.

#### **Data Types**

The data widths supported by the processor are 32-bit words, 16-bit halfwords, and 8-bit bytes, and only unsigned data types.

#### **Addressing Modes**

The instruction set supports two vector addressing modes:

- 1. Unit stride access, when values are found in adjacent locations.

- 2. Constant stride access, when logically adjacent values are separated by a constant number of bytes.

#### Flag Register Use

Almost all instruction can specify one of two vector mask registers in the opcode to use as an execution mask. By default, vfmask0 is used as the vector mask. Writing a value of 0 into the mask register will cause the VP to be disabled for operations that use the mask. Some instructions, such as flag logical operations, are not maskable.

#### Instructions

Table 4.4 describes the possible qualifiers in the assembly code describing each instruction.

| Qualifier | Meaning             | Description                                                 |

|-----------|---------------------|-------------------------------------------------------------|

| op.vv     | Vector-vector       | Vector arithmetic instructions may take one source operand  |

| op.vs     | Scalar-vector       | from a scalar register. A vector-vector operation takes two |

|           |                     | two vector source operands from the vector register file; a |

|           |                     | vector-scalar operation takes second operand from a         |

|           |                     | scalar register file.                                       |

| op.b      | 1B Byte             | All vector memory instructions need to specify the width    |

| op.h      | 2B Halfword         | of integer data, which may be 1, 2, or 4 bytes.             |

| op.w      | 4B Word             |                                                             |

| op.1      | vfmask1 as the mask | The vector mask is taken from vfmask0 by default. This      |

|           |                     | qualifier selects vfmask1 as the vector mask.               |

| $T_{-} = 1 + 1 + 4 + 4$ | T           |          | £   |           |

|-------------------------|-------------|----------|-----|-----------|

| 1able 4.4:              | Instruction | quaimers | IOL | opcode op |

|                         |             |          |     |           |

The instruction set includes the following categories of instructions: